back to home▼

|

||||

| Professor | Student | Alumni |

Notice | Lecture | Journal | University | ||

|

||||

Nano FET CMOSFET has been dramatically scaling down into nano ranges. |

||||

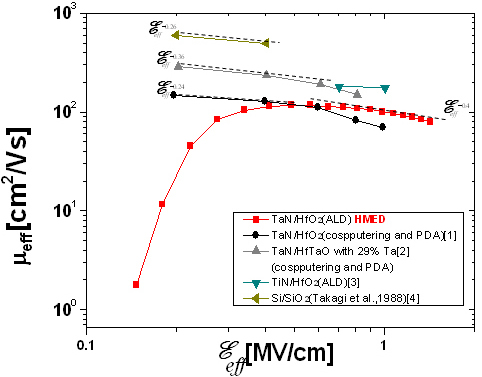

Fig 1. Measured mobility of Metal/high-k FET (20/30)

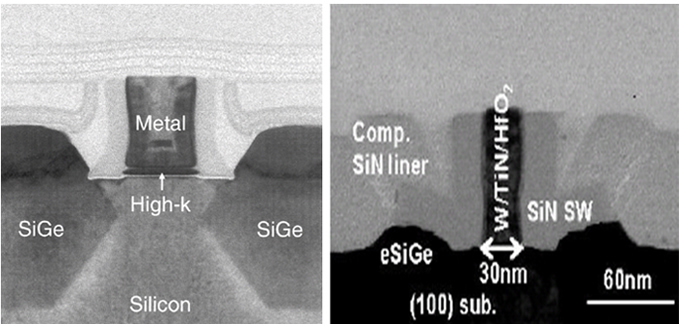

Fig 2. TEM micrograph of high-k + metal gate N/P MOS transistors (Intel, sony 2007)

|

||||

|

||||

|

||||